### **Applications**

- Down- and Up-Converters

- Measurement equipment

- Radar

- General Purpose Frequency Generation

- Radiation hard version available

# IMST NOV8G12 Single Chip Synthesizer v1.0

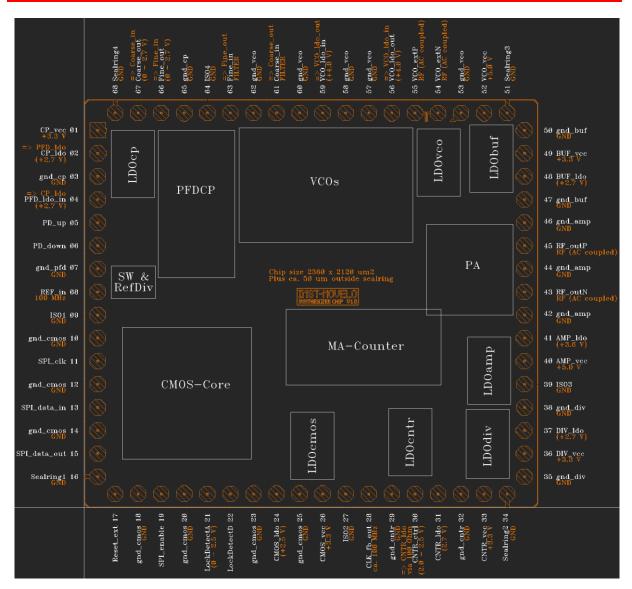

Chip size 2.46 x 2.22 mm<sup>2</sup>

#### **Product Features**

- 8-12 GHz, external VCO possible (1.5-12 GHz in preparation)

- +3 dBm Output Power (single ended)

- 1 mHz Fractional-N accuracy

- -100 dBc/Hz typ. in loop phase noise (10 KHz offset)

- No reference spurs

- 4-wire SPI (Read/Write, Master/Slave)

- XILINKS Prom option

#### **General Description**

The IMST NOV8G12 is an 8-12 GHz fractional-N synthesizer, which can be programmed in mHz steps. The synthesizer can be programmed using a SPI (read/write mode). It features an output amplifier and provides a differential output power of +6 dBm (diff.) over the entire frequency range.

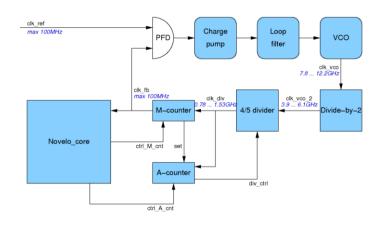

## **Block Diagram**

## **Ordering Information**

| Part No.   | Description                  |

|------------|------------------------------|

| NOV8G12    | 8-12 GHz Synthesizer         |

| NOV8G12RH  | Radiation hard variant       |

| NOV8G12EB  | Evaluation Board             |

| NOV8G12PUD | PFD output for active filter |

Standard order size is 25 chips.

# **Chip Pin Description**

| Pin# | Label        | Туре | Value    | Description                                                                                                     |

|------|--------------|------|----------|-----------------------------------------------------------------------------------------------------------------|

| 01   | CP vcc       |      | +3.3 V   | External supply voltage (type A).                                                                               |

| 02   | CP Ido       | LDO  | +2.7 V   | LDO voltage regulator output (generated on-chip).                                                               |

| 03   | gnd_cp       | GND  |          |                                                                                                                 |

| 04   | PFD_ldo_in   | IN   | +2.7 V   | External connection to CP_ldo needed.                                                                           |

| 05   | PD_up        | OUT  |          | Phase detection output 'UP'. Turns from HIGH to LOW if reference frequency is ahead of feedback frequency.      |

| 06   | PD_down      | OUT  |          | Phase detection output 'DOWN'. Turns to LOW if feedback frequency is ahead of reference frequency.              |

| 07   | gnd pfd      | GND  |          |                                                                                                                 |

| 08   | REF_in       | IN   | 100 MHz  | External reference frequency. The input is DC coupled,<br>an external decoupling capacitor (1 nF) is necessary. |

| 09   | ISO1         | GND  |          | Ground connection for on-chip guard rings.                                                                      |

| 10   | gnd_cmos     | GND  |          |                                                                                                                 |

| 11   | SPI_clk      | IN   | 12.5 MHz | Clock for the Serial Peripheral Interface (SPI).                                                                |

| 12   | gnd_cmos     | GND  |          |                                                                                                                 |

| 13   | SPI_data_in  | IN   |          | SPI data input.                                                                                                 |

| 14   | gnd_cmos     | GND  |          |                                                                                                                 |

| 15   | SPI_Data_out | OUT  |          | SPI data output.                                                                                                |

| 16   | Sealring1    | GND  |          | Ground connection for on-chip seal rings.                                                                       |

| 17   | Reset_ext    | IN   |          | External reset (LOW active, HIGH at normal operation).                                                          |

| 18   | gnd_cmos     | GND  |          |                                                                                                                 |

| 19   | SPI_enable   | IN   |          | SPI enable (LOW active).                                                                                        |

| 20   | gnd_cmos     | GND  |          |                                                                                                                 |

| 21   | LockDetectA  | OUT  |          | Analog PFD lock detect output voltage (0 to 2.5 V).                                                             |

| 22   | LockDetectD  | OUT  |          | Digital lock detect output (also provided via SPI).                                                             |

| 23   | gnd cmos     | GND  |          |                                                                                                                 |

| 24   | CMOS Ido     | LDO  | +2.5 V   |                                                                                                                 |

| 25   | <br>gnd_cmos | GND  |          |                                                                                                                 |

| 26   | CMOS_vcc     | IN   | +3.3 V   | External supply voltage (type A).                                                                               |

| 27   | ISO2         | GND  |          |                                                                                                                 |

| 28   | CLK fb out   | OUT  |          | Optional feedback frequency output.                                                                             |

| 29   | gnd cntr     | GND  |          |                                                                                                                 |

| 30   | CNTR_ctrl    | IN   | +2.5 V   | Best connected to CNTR_ldo via 100 $\Omega$ externally.                                                         |

| 31   | <br>CNTR_ldo | LDO  | +2.7 V   |                                                                                                                 |

| 32   | <br>gnd_cntr | GND  |          |                                                                                                                 |

| 33   | CNTR_vcc     | IN   | +3.3 V   | External supply voltage (type A).                                                                               |

| 34   | Sealring2    | GND  |          |                                                                                                                 |

| 35   | gnd_div      | GND  |          |                                                                                                                 |

| 36   | DIV_vcc      | IN   | +3.3 V   | External supply voltage (type A).                                                                               |

| 37   | DIV_ldo      | LDO  | +2.7 V   |                                                                                                                 |

| 38   | gnd_div      | GND  |          |                                                                                                                 |

# IMST NOV8G12 Single Chip Synthesizer v1.0

#### PRELIMINARY INFORMATION

| Pin# | Label       | Туре | Value         | Description                                                                                                                                                                                                      |

|------|-------------|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39   | ISO3        | GND  |               |                                                                                                                                                                                                                  |

| 40   | AMP_vcc     | IN   | +5.0 V        | External supply voltage (type B).                                                                                                                                                                                |

| 41   | AMP_ldo     | LDO  | +3.6 V        |                                                                                                                                                                                                                  |

| 42   | gnd_amp     | GND  |               |                                                                                                                                                                                                                  |

| 43   | RF_outN     | OUT  |               | Differential RF output (N), AC coupled to on-chip voltages, but 1 K $\Omega$ to GND for ESD protection.                                                                                                          |

| 44   | gnd_amp     | GND  |               |                                                                                                                                                                                                                  |

| 45   | RF_outP     | OUT  |               | Differential RF output (P), AC coupled to on-chip voltages, but 1 K $\Omega$ to GND for ESD protection.<br>Single ended output is possible (termination of the unused port via 50 $\Omega$ load is recommended). |

| 46   | gnd_amp     | GND  |               |                                                                                                                                                                                                                  |

| 47   | gnd_buf     | GND  |               |                                                                                                                                                                                                                  |

| 48   | BUF_ldo     | LDO  | +2.7 V        |                                                                                                                                                                                                                  |

| 49   | BUF_vcc     | IN   | +3.3 V        | External supply voltage (type A).                                                                                                                                                                                |

| 50   | gnd_buf     | GND  |               |                                                                                                                                                                                                                  |

| 51   | Sealring3   | GND  |               |                                                                                                                                                                                                                  |

| 52   | VCO_vcc     | IN   | +5.0 V        | External supply voltage (type B).                                                                                                                                                                                |

| 53   | gnd_vco     | GND  |               |                                                                                                                                                                                                                  |

| 54   | VCO_extN    | IN   |               | Differential external RF input (N), AC coupled to on-chip voltages, but 1 K $\Omega$ to GND for ESD protection.                                                                                                  |

| 55   | VCO_extP    | IN   | +5 dBm        | Differential external RF input (P), AC coupled to on-chip voltages, but 1 K $\Omega$ to GND for ESD protection.<br>Single ended input possible (keep unused port floating).                                      |

| 56   | VCO_ldo_out | LDO  | +4.0 V        |                                                                                                                                                                                                                  |

| 57   | gnd_vco     | GND  |               |                                                                                                                                                                                                                  |

| 58   | gnd_vco     | GND  |               |                                                                                                                                                                                                                  |

| 59   | VCO_ldo_in  | IN   | +4.0 V        | External connection to VCO_ldo_out necessary.                                                                                                                                                                    |

| 60   | gnd_vco     | GND  |               |                                                                                                                                                                                                                  |

| 61   | Coarse_in   | IN   | 0 to<br>2.7 V | Coarse voltage control input for on-chip VCOs.<br>External connection to Fine_out via filter needed.                                                                                                             |

| 62   | gnd_vco     | GND  |               |                                                                                                                                                                                                                  |

| 63   | Fine_in     | IN   | 0 to<br>2.7 V | Fine voltage control input for on-chip VCOs.<br>External connection to Fine_out via filter needed.                                                                                                               |

| 64   | ISO4        | GND  |               |                                                                                                                                                                                                                  |

| 65   | gnd_cp      | GND  |               |                                                                                                                                                                                                                  |

| 66   | Fine_out    | OUT  |               | Fine charge pump output current.                                                                                                                                                                                 |

| 67   | Coarse_out  | OUT  |               | Coarse charge pump output current.                                                                                                                                                                               |

| 68   | Sealring4   | GND  |               |                                                                                                                                                                                                                  |

The given values are nominal. Please refer to the table 'recommended operating' for valid ranges. IN: Input port OUT: output port GND: Direct down bond to the carrier board ground plane (keep bonds short)

LDO: Voltages generated on-chip, off-chip shunt capacitors needed (100 pF, 100 nF, and 2.2  $\mu$ F in SMD 0201)

#### Absolue Maximum Ratings

| Parameter                   | Rating        |

|-----------------------------|---------------|

| Storage Temperature         | -65 to 150 °C |

| RF Input Power              | +13 dBm       |

| Device voltage              | +3.6 V/+5.5 V |

| SPI I/O                     | +3.6 V        |

| Operation of this device of |               |

parameter ranges given above may cause permanent damage.

### **Recommended Operating**

| Parameter        | Min   | Тур  | Max  | Units |

|------------------|-------|------|------|-------|

| Temperature      | -40   | +23  | +85  | °C    |

| Device Voltage A | +3.0  | +3.3 | +3.6 | V     |

| Device Voltage B | +4.5  | +5.0 | +5.5 | V     |

| SPI I/O          | +2.25 | +3.3 | +3.6 | V     |

Electrical specifications are measured at specified test conditions. Specifications are not guaranteed over all recommended operating conditions.

### **Electrical Specifications**

Test conditions unless otherwise noted:  $V_{\text{DD}}{=}\,{+}\,5$  V, Temp=+25 °C, 50  $\Omega$  system.

| Parameter            |              | Conditions                                                                                                                                                                              | Min | Тур | Max  | Units  |

|----------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|--------|

| Operation Fre        | quency Range |                                                                                                                                                                                         | 8   |     | 12   | GHz    |

| Frequency step       | С            |                                                                                                                                                                                         | 0.1 |     |      | Hz     |

| Output power         |              | Differential, single ended 3 dB less                                                                                                                                                    |     | +5  |      | dBm    |

| SSB phase noi        | se           |                                                                                                                                                                                         |     |     |      |        |

|                      | 10 Hz        |                                                                                                                                                                                         |     |     | -70  | dBc/Hz |

|                      | 100 Hz       |                                                                                                                                                                                         |     |     | -80  | dBc/Hz |

|                      | 1 KHz        |                                                                                                                                                                                         |     |     | -90  | dBc/Hz |

| Offset               | 10 KHz       |                                                                                                                                                                                         |     |     | -95  | dBc/Hz |

|                      | 100 KHz      |                                                                                                                                                                                         |     |     | -100 | dBc/Hz |

|                      | 1 MHz        |                                                                                                                                                                                         |     |     | -120 | dBc/Hz |

|                      | 10 MHz       |                                                                                                                                                                                         |     |     | -140 | dBc/Hz |

| AM Noise             |              | At 5 MHz offset                                                                                                                                                                         |     |     | -115 | dBc/Hz |

| Harmonics            |              |                                                                                                                                                                                         |     |     | -40  | dBc    |

| Reference Spu        | rs           |                                                                                                                                                                                         |     |     | -145 | dBc    |

| FOM <sub>FLOOR</sub> |              | Complete loop<br>$PN_{FLOOR} = FOM_{FLOOR} + 10\log(f_{REF}/Hz) + 20\log(f_{REF}/f_{REF})$<br>with $f_{RF}$ = synthesizer output frequency<br>and $f_{RFF}$ = reference input frequency |     |     | -225 | dBc/Hz |

| FOM <sub>FLOOR</sub> |              | PFD only                                                                                                                                                                                |     |     | -229 | dBc/Hz |

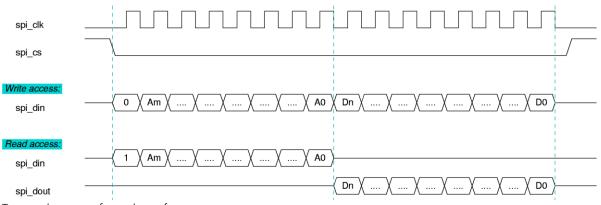

# **Timing Diagram and Registers**

Timing diagram of serial interface

**Control registers** (address range "0000" to "1011" registers are read-write).

| Address                 | Bit  | Name              | Function                                                                                                                                                                                           | Default |

|-------------------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| "0000"<br>Divisor_reg_0 | 150  | divisor(35:20)    | M/A-counter divisor bits 70, -18<br>Default divider setting is 45.0, with a<br>minimum of 12 and a maximum of 255.                                                                                 | 0x2D00  |

|                         |      |                   | The M/A settings are calculated from the programmable integer divider value D:                                                                                                                     |         |

|                         |      |                   | $D = 5A + 4(M + 1 - A) \text{ and } A \le M + 1$<br>A is calculated from the two LSB of D (max. 3)                                                                                                 |         |

|                         |      |                   | For example results the default divider setting (D = 45) in M = 10 and A = 1                                                                                                                       |         |

| "0001"<br>Divisor_reg_1 | 150  | divisor(19:4)     | Divisor bits -924                                                                                                                                                                                  | 0x0000  |

| "0010"                  | 1512 | divisor(3:0)      | Divisor bits -2528                                                                                                                                                                                 | "0000"  |

| Divisor_reg_2           | 110  | unused            |                                                                                                                                                                                                    |         |

| "0011"<br>Config. rog   | 158  | unused            |                                                                                                                                                                                                    |         |

| Config_reg              | 7    | reset_sd          | Low-active reset for Sigma Delta Modulator<br>(SDM)                                                                                                                                                | "0"     |

|                         | 65   | sd_mux            | Number of SDM accumulator stages:<br>"00", "01", "10", "11" = 1, 2, 3, 4                                                                                                                           | "00"    |

|                         | 4    | ref_div_bypass_en | Enable for reference clock bypass switch                                                                                                                                                           | "O"     |

|                         | 30   | ref_div_ctrl      | Divisor for reference clock divider (015)<br>O activates the divider bypass within the<br>reference divider. 1 divides by one.                                                                     | "0000"  |

| "0100"<br>Preload_reg   | 150  | Preload           | Preloads first accumulator bits -116                                                                                                                                                               | 0x0000  |

| "0101"                  | 1514 | Unused            |                                                                                                                                                                                                    |         |

| CP_reg                  | 1312 | cp_test           | Test modus for charge pump currents.<br>PFD switched to constant outputs.<br>"01" 'UP' current activated, also PD_up<br>"10" 'DOWN' current and PD_down on<br>"11" both activated, 'UP' and 'DOWN' | "00"    |

|                         | 11   | cp_fine_en        | Enable for charge pump fine current                                                                                                                                                                | "]"     |

|                         | 10   | cp_coarse_en      | Enable for charge pump coarse current<br>Coarse charge current is 500 µA                                                                                                                           | "]"     |

|                         | 95   | cp_fine           | Charge pump fine current ( <i>lcpf</i> ) settings<br>MSB 4 mA, 2 mA, 1 mA, 500 µA, 250 µA                                                                                                          | "01000" |

|                         | 40   | Unused            |                                                                                                                                                                                                    |         |

| "0110"<br>Offeet reg    | 1510 | Unused            |                                                                                                                                                                                                    |         |

| Offset_reg              | 95   | offset_fine       | Fine offset current losf = $n^{1}$ cpf/50; $n 031$                                                                                                                                                 | "00001" |

|                         | 40   | offset_coarse     | Coarse offset current setting<br>losc = $n^*100 \ \mu A; n \ 031$                                                                                                                                  | "00001" |

# IMST NOV8G12 Single Chip Synthesizer v1.0

#### PRELIMINARY INFORMATION

| Address        | Bit  | Name           | Function                                                                                                                               | Default |

|----------------|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|

| "0111"<br>\/CO | 158  | Unused         |                                                                                                                                        |         |

| VCO_reg        | 7    | ldo_vco_en     | Enable for VCO LDO                                                                                                                     | "]"     |

|                | 63   | vco_band_ctrl  | Band selection for internal VCO arrays.<br>In the current configuration, 8 bands are used<br>from "0000" (lowest) to "0111" (highest). | "0011"  |

|                | 20   | vco_ctrl       | VCO control. "000", "001", "010" enables<br>internal low, medium, or high band VCO.<br>"011" enables external VCO path                 | "000"   |

| Address        | Bit  | Name           | Function                                                                                                                               | Default |

| "1000"         | 158  | unused         |                                                                                                                                        |         |

| Enable_reg     | 7    | lock_detect_en | Enable for lock detect buffer                                                                                                          | "O"     |

|                | 6    | ldo_div_en     | Enable for pre-divider LDO                                                                                                             | "]"     |

|                | 5    | ldo_buf_en     | Enable for VCO output chain LDO                                                                                                        | "]"     |

|                | 4    | ldo_amp_en     | Enable for output power amplifier LDO                                                                                                  | "]"     |

|                | 3    | pfd_vout_en    | Enable for PFD voltage output                                                                                                          | "O"     |

|                | 2    | pfd_en         | Enable for PFD                                                                                                                         | "]"     |

|                | 1    | div_en         | Enable for feedback clock pre-divider                                                                                                  | "]"     |

|                | 0    | clk_fb_out_en  | Enable for feedback clock output                                                                                                       | "0"     |

| "1001"         | 1512 | Unused         |                                                                                                                                        |         |

| GPO_reg        | 118  | gpo_default_1  | General purpose outputs with default "1"                                                                                               | "1111"  |

|                | 74   | Unused         |                                                                                                                                        |         |

|                | 31   | gpo_default_0  | General purpose outputs with default "0"                                                                                               | "0000"  |

|                | 0    | lockdetectD_en | Enables digital lock detect output buffer                                                                                              | "O"     |

### Status registers (address range "1100" to "11111" registers are read-only).

| Address    | Bit  | Name        | Function                                         | Default |

|------------|------|-------------|--------------------------------------------------|---------|

| "1100"     | 158  | gpi         | General purpose inputs                           |         |

| Status_reg | 74   | version     | Version number, increases on full mask run       | "0001"  |

|            | 30   | subversion  | Subversion number, increases on metal change run | "0000"  |

| "1101"     | 1511 | unused      |                                                  |         |

| Error_reg  | 10   | lock_detect | PLL lock detect                                  |         |

|            | 90   | error_cnt   | Triple mode error count                          |         |

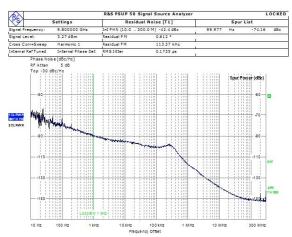

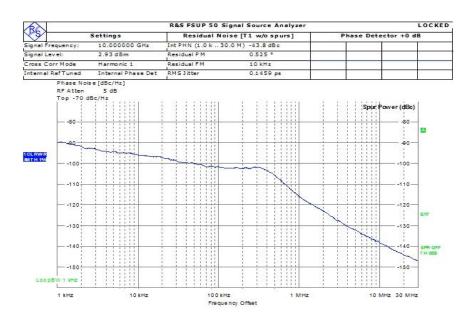

#### **Typical Measurement Results**

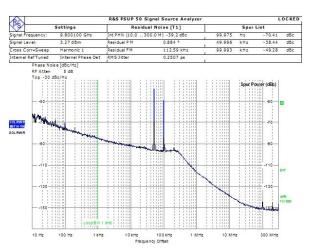

Integer mode performance at 9.8 GHz including all spurs (+20 °C). Residual phase modulation is 0.6°.

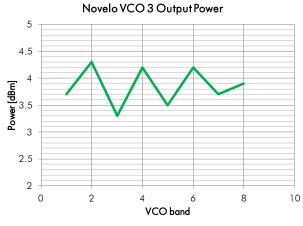

NOVELO output power versus VCO band.

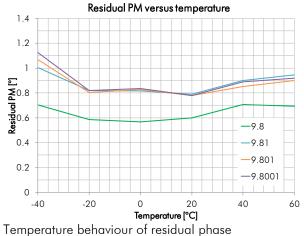

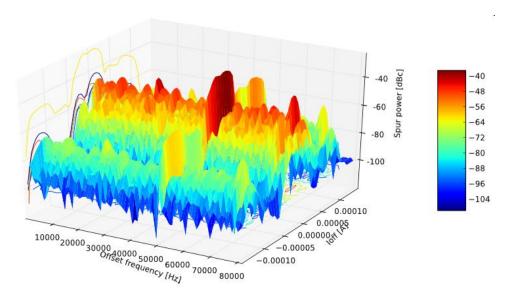

Fractional mode performance at 9.8001 GHz including all spurs (+20 °C). Residual phase modulation is 0.88°.

modulation. Variation is 0.1° over 100 K.

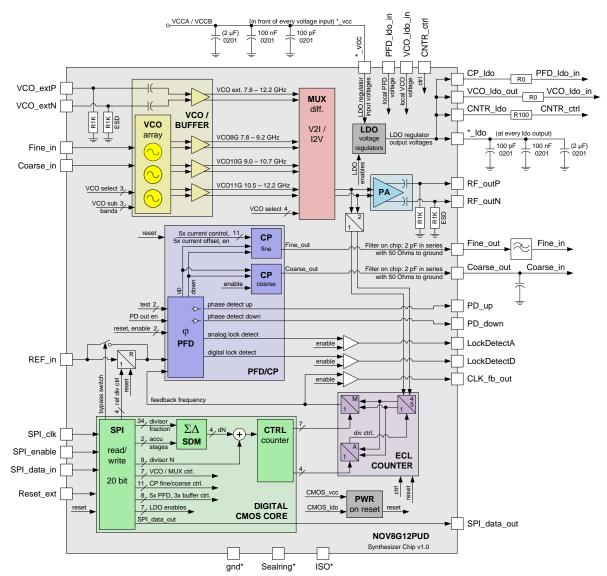

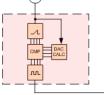

#### Functional Description and Functional Block Diagram

NOV8G12 is a full functional fractional-N synthesizer. The frequency generation is performed internally, by an array of voltage controlled oscillators with 3 VCOs covering the frequency range of 8 to 12 GHz. In parallel, the connection of an external RF source is possible. Via multiplexer, the buffered VCO outputs are connected to the output amplifier and a feedback path with prescaler (divide-by-two circuit) and ECL based 4/5 dual modulus divider in combination with a master and assistant (M/A) counter. The ECL-counter output is feed to a phase frequency detector (PFD), which generates voltage up- and down-pulses depending on the down-divided signal phase compared to the reference frequency phase. The following charge pump (CP) converts these pulses into up- and down-currents, charging external loop filter capacitances. The voltages across the capacitances regulate the VCO output frequency – the loop (PLL) is closed.

The synthesizer can be operated in two modes, integer and fractional. During integer mode, a fixed divider ratio is applied to the divider chain. This way, the output frequency can be adjusted to multiple of divider ratio and reference frequency (e.g. 2\*45\*100MHz=9GHz). Employing a programmable sigma delta modulator (SDM) based on CMOS logic, dynamic changes of the main divider factor N are performed (Gauss distribution). This results in a fractional main divider factor Q with the possibility to access frequencies down to 1 mHz step size at moderate spur and quantization noise levels.

Detailed functional block diagram

# IMST NOV8G12 Single Chip Synthesizer v1.0

PRELIMINARY INFORMATION

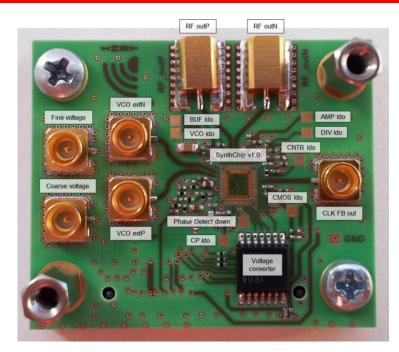

## NOV8G12EB Evaluation Board

Synthesizer board with connectors

Main board with voltage supply, crystal reference clock and socket for synthesizer board

## Bill of Material - NOV8G12EB

| Reference Designation                      | Value                                                       |

|--------------------------------------------|-------------------------------------------------------------|

| Crystek low phase noise reference clock    | 100 MHz, -160 dBc/Hz phase noise                            |

| Voltage regulators from single +5 V supply | 5 V, 3.3 V and 2.5 V                                        |

| SMD components                             | Various values (capacitances and resistors for loop filter) |

| RF connectors                              | Various                                                     |

## Typical Performance

Test conditions unless otherwise noted:  $V_{DD}$ =+5 V, Temp=+25 °C, 50  $\Omega$  system.

| Parameter                  |      | Турісс | ıl Value | Units |        |

|----------------------------|------|--------|----------|-------|--------|

| Frequency                  | 8    | 9      | 10       | 12    | GHz    |

| Output power <sup>1</sup>  | +3   | +3     | +3       | +3    | dBm    |

| Phase noise @ 1 MHz offset | -120 | -120   | -120     | -120  | dBc/Hz |

| Power consumption          | <1.5 | <1.5   | <1.5     | <1.5  | W      |

Notes:

1. Output power values in the table above include board losses. (approx. =1...2 dB at 12 GHz).

## Performance Plots

Test conditions unless otherwise noted:  $V_{DD}$ =+5 V, Temp=+25 °C, 50  $\Omega$  system.

Residual phase modulation at 10 GHz is 0.5°. Optimized loop filter setting and optimized charge pump current/offset current settings.

## **Simulation Tool**

Precise simulation of phase noise and spurs

### **Radiation Tests**

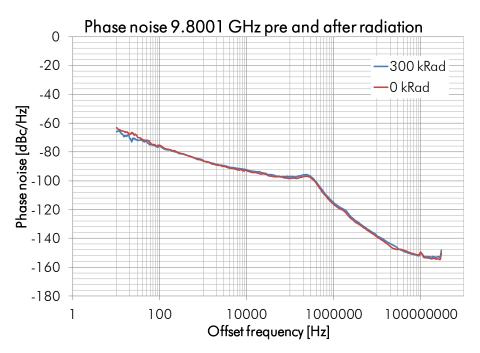

NOVELO fractional mode before (red) and after TID (blue) of 300 kRad.

#### Evaluation Board PCB Information

Evaluation main board is FR4 multilayer. Evaluation synthesizer board is Rogers multilayer. Evaluation board comes with controlling software (read/write). IMST also offers embedded board web server based software.

## **Chip Marking and Dimensions**

Chip size is 2.46 x 2.22 mm<sup>2</sup>. Pad one (square) is upper left corner (CP\_vcc).

Notes:

- 1. All dimensions are in millimeters. Angles are in degrees.

- 2. Dimension and tolerance formats conform to ASME Y14.4M-1994.

- 3. The terminal #1 identifier and terminal numbering conform to JESD 95-1 SPP-012.

- 4. Contact plating: NiPdAu

# IMST NOV8G12 Single Chip Synthesizer v1.0

## **PCB** Mounting Pattern

#### TBD

Notes:

- 1. All dimensions are in millimeters. Angles are in degrees.

- 2. Use 1 oz. copper minimum for top and bottom layer metal.

- 3. Vias are required under the backside paddle of this device for proper RF/DC grounding and thermal dissipation.

- 4. Do not remove or minimize via hole structure in the PCB. Thermal and RF grounding is critical.

- 5. We recommend a 0.35mm (#80/.0135") diameter bit for drilling via holes and a final plated thru diameter of 0.25 mm (0.10").

- 6. Ensure good package backside paddle solder attach for best electrical and thermal performance.

Compatible with both lead-free (260 °C maximum reflow temperature) and tin/lead (245 °C maximum

This part is compliant with EU 20M/65/EC RoHS

directive (Restrictions on the Use of Certain

Hazardous Substances in Electrical and Electronic

Halogen Free (Chlorine, Bromine)

This product also has the following attributes:

TBBP-A  $(C_{15}H_{12}Br_4O_2)$  Free

reflow temperature) soldering processes.

**Solderability**

Contact plating: NiPdAu

**RoHs** Compliance

Lead Free

Antimony Free

**PFOS Free**

SVHC Free

Equipment).

#### Product Compliance Information

#### **ESD Sensitivity Ratings**

Caution! ESD-Sensitive Device

| ESD Rating: | Class 1A                        |

|-------------|---------------------------------|

| Value:      | Passes $\geq 250$ V to $<500$ V |

| Test:       | Human Body Model (HBM)          |

| Standard:   | JEDEC Standard JESD22-A114      |

| ESD Rating: | Class IV                        |

| Value:      | Passes $\geq$ 1000 V            |

| Test:       | Charged Device Model (CDM)      |

| Standard:   | JEDEC Standard JESD22-C101      |

#### **MSL** Rating

MSL Rating: Level 3 Test: 260 °C convection reflow Standard: JEDEC Standard IPC/JEDEC J-STD-020

# Product Highlights

## • Dual loop concept (coarse and fine regulating loop)

- Complete analog temperature compensation on chip

- 3.6 V resistant SPI I/O pins

- Externally noise filtered voltage regulators on chip

- ESD protection for all pins

- Patented reference generator (WO 2013/167196 A1) in development. This will eliminate all fractional spurs.

- High quality simulation tool available (SpurSIM)

- Programmable charge pump and offset currents (both coarse and fine)

- Chip aspect ratio 1:1 for easy packaging

- 1.5-12 GHz version in preparation (internal VCOs)

- External VCO and external active loop filter possible

- Programmable Delta Sigma modulator (1, 2, 3 or 4 stages)

- No SDM quantization noise

- Noise optimized output multiplexer and amplifier for low RF noise

- On-chip shielded triplate lines and noise shields

- Level shifters between voltage domains

Patented reference generator concept (WO 2013/167196 A1)

#### Contact Information

For the latest specifications, additional product information, worldwide sales and distribution locations, and information about IMST:

Web: www.imst.com, Fon: +49.2842.891.0 Email: caontact@imst.com, Fax: +49.2842.981.199

For technical questions and application information:

Email: contact@imst.com

#### Important Notice

The information contained herein is believed to be reliable. IMST makes no warranties regarding the information contained herein. IMST assumes no responsibility or liability whatsoever for any of the information contained herein. The information contained herein is provided "AS IS, WHERE IS" and with all faults, and the entire risk associated with such information is entirely with the user. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for IMST products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information.

IMST products are not warranted or authorized for use as critical components in medical, life-saving, or lifesustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.